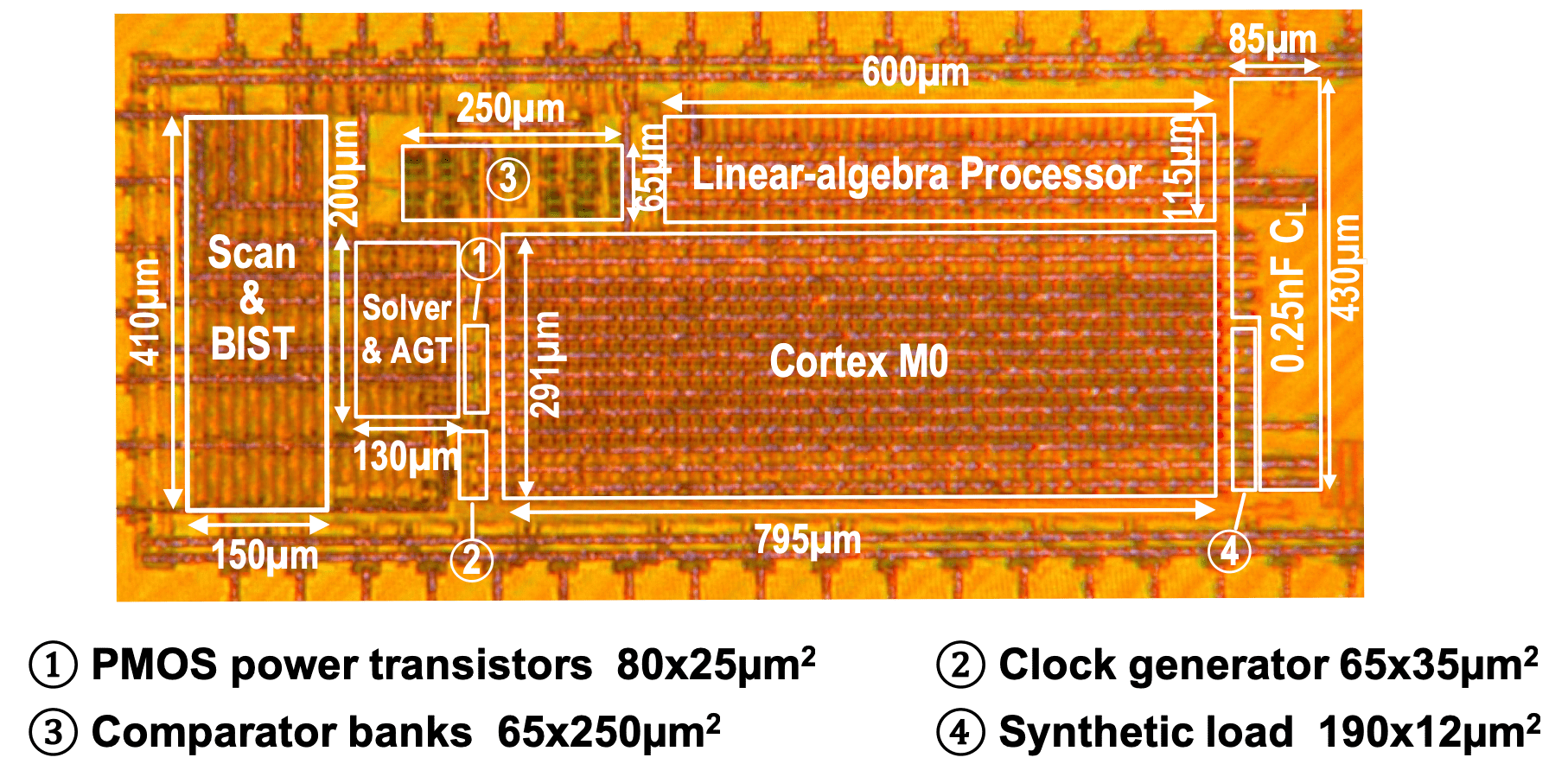

Chi-Hsiang Huang [ISSCC 2022]

“Regenerative Breaking” for Energy-Efficient Sleep in Duty-Cycled Low-Power SoCs.

Fahim ur Rahman [ISSCC 2019]

Computationally-Enabled Total Energy Minimization under Performance Requirements for a Volt-age Regulated 0.38–¬0.58V Microprocessor in 65nm CMOS

Arindam Mandal [CICC 2021]

A 46-channel computationally guided vector stimulator for low-latency targeted neural stimulation with 50mV worst case common mode artifact in 180nm CMOS

Xun Sun-UniCaP1 [ISSCC 2018]

A Combined All-Digital PLL-Buck Slack Regulation System with Autonomous CCM/DCM Transition Control and 82% Average Voltage-Margin Reduction in a 0.6-to-1.0V Cortex-M0 Processor

Visvesh Sathe [VLSI Symp, JSSC]

RF2: The first-ever fully integrated resonant clocked datapath.

Visvesh Sathe [CICC, JSSC]

RF1: Single-phase resonant clocked ASIC with programmable operating frequency of 0.8GHz-1.2GHz

Chi-Hsiang Huang [ISSCC 2021]

The first SIMO regulated SoC with adaptive clocking and Dynamic Droop Allocation to address transient response and ripple induced Vdd margins in 65nm CMOS

Xun Sun [VLSI 2020]

UniCaP-2, aggressive Vdd margin recovery and rapid transient response through voltage and phase error feedback

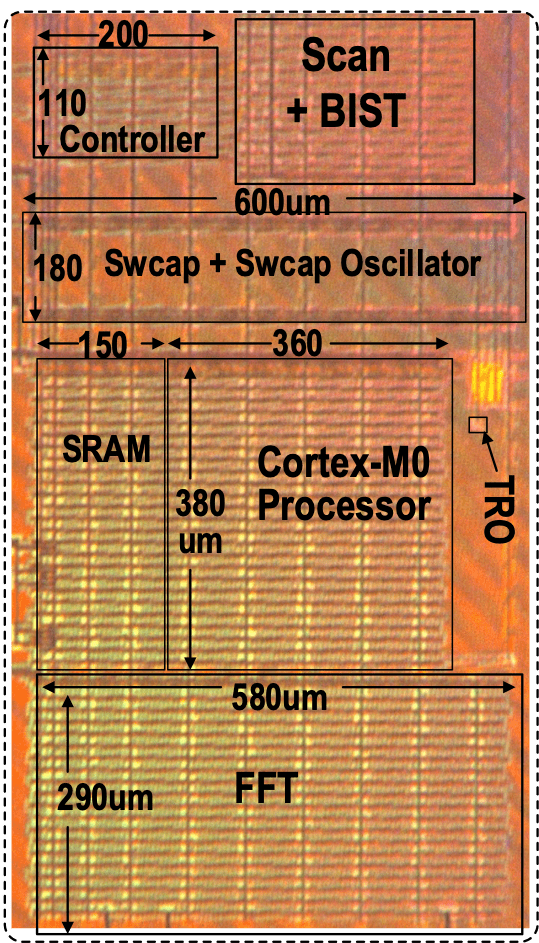

Fahim ur Rahman [VLSI 2018]

An All-Digital Unified Clock Frequency and Switched-Capacitor Voltage Regulator for Variation Tolerance in a Sub-Threshold ARM Cortex M0 Processor

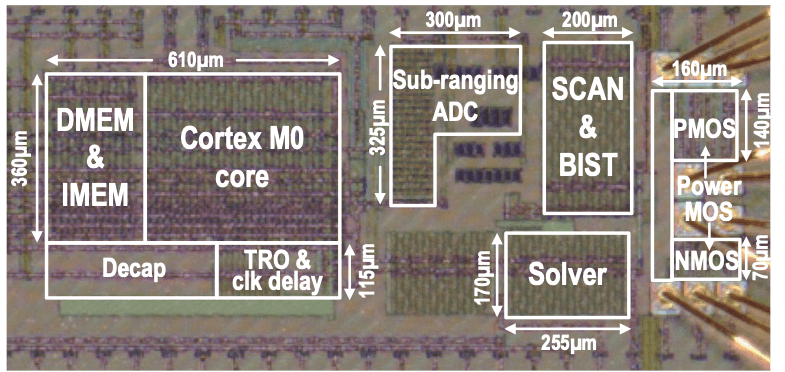

William A. Smith [ESSCIRC] [TBIOCAS]

A prototype demonstrating optimized ECoG signal chain design with reduced noise and ADC requirements, resolved from specific characteristics of ECoG signals.

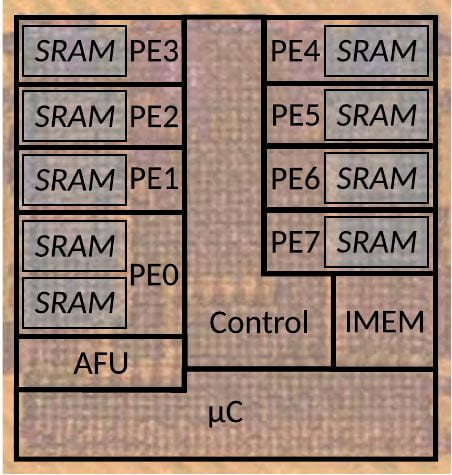

Sung Kim

Techniques for “learning around” largely-static memory errors caused by aggressive memory-voltage overscaling, demonstrated on a low-power DNN accelerator SoC.

Xun Sun - UniCaP 2 [VLSI 2020]

The first Model Predictive Controlled integrated buck regulator in 65nm CMOS

Xun Sun [VLSI 2020]

UniCaP-2, aggressive Vdd margin recovery and rapid transient response through voltage and phase error feedback

William A. Smith [VLSI Symp.]

A highly-multiplexed, delta-encoded mixed-signal biopotential recording architecture with common and differential-mode artifact suppression.

Fahim U. Rahman [ISSCC]

The first demonstration of truly voltage-scalable quasi-resonant clocking.

Fahim U. Rahman [ISSCC]

The first-ever demonstration of computational locking for ADPLLs, a radically different way of achieving lock to advance cold-start lock-times by nearly an order of magnitude.